The ARM is a 32-bit reduced instruction set computer (RISC) instruction set architecture (ISA) developed by ARM Holdings. It was known as the Advanced RISC Machine, and before that as the Acorn RISC Machine. The ARM architecture is the most widely used 32-bit ISA in terms of numbers produced. They were originally conceived as a processor for desktop personal computers by Acorn Computers, a market now dominated by the x86 family used by IBM PC compatible and AppleMacintosh computers.

The ARM Cortex-M3

The ARM Cortex family is a new generation of processors that has a standard CPU and system architecture. Unlike other ARM CPUs, the Cortex family is a complete processor core in itself.

It comes in three series:

A series: For high end applications, using complex OS and user

applications. It supports ARM, Thumb and Thumb-2

instruction sets.

R series: They follow more of a RT system profile. They too

supports ARM, Thumb and Thumb-2 instruction sets.

M series: For microcontroller applications, and other

cost-sensitive projects. It supports only Thumb-2

instruction set.

There is a relative performance level for all these devices, ranging from 1-8. The highest level for M series is 3.

The ARM Cortex-M3 provides the entire heart of a microcontroller, including timer, memory map, interrupt system, etc.

It has a Harvard Architecture, with about 4 GB total address space.

Operating Modes

In privileged mode, the CPU has access to the full instruction set.

In unprivileged mode, xPSR related functions and access to most registers in the Cortex processor control space are disabled.

|

| Fig 1. The Cortex-M3 operating modes |

Programmer’s Model

The Cortex CPU RISC processor has a load/store architecture. To perform data processing operations, operands must be loaded into a central register file, and the data operations are performed on these registers, and the result stored back to memory.

|

| Fig 2. The load/store architecture of Cortex-M3 |

Register File

There are sixteen 32-bit registers in the processor register file, with an extra 32-bit xPSR (Program Status Register).

|

| Fig 3. The Cortex-M3 register file and xPSR |

There are two stacks, main stack and process stack, to support the two operating modes. Register R15 is the Program Counter (PC).

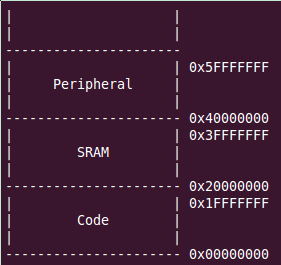

Memory Map

The memory map for the code area, SRAM area, and the peripheral devices are shown below.

|

| Fig 4. A portion of the Cortex-M3 memory map |

Features

1. Unaligned memory access - The Cortex-M3 can make unaligned memory access, which ensures that SRAM is efficiently used.

2. Bit Banding - By this technique, direct bit manipulation can be performed on sections of peripheral and SRAM memory spaces, without the need for any special instructions (normal bit manipulations require READ, MODIFY, WRITE which is expensive in terms of number of cycles).

3. Nested Vector Interrupt Controller (NVIC) - It is a standard unit within the Cortex core, thus making the process of porting the code to different microcontrollers easier. It is designed to support nested interrupts and there are 16 levels of priority.

By the interrupt preemption technique, high priority interrupts can preempt low priority ones. By the tail chaining technique, successive interrupts can be added to the tail queue, thus reducing the latency in handling those interrupts.